#

# Am79C930

# PCnet<sup>™</sup>-Mobile Single-Chip Wireless LAN Media Access Controller

## DISTINCTIVE CHARACTERISTICS

- Capable of supporting the IEEE 802.11 standard (draft)

- Supports the Xircom Netwave<sup>™</sup> media access control (MAC) protocols

- Supports MAC layer functions

- Individual 8-byte transmit and 15-byte receive FIFOs

- Integrated intelligent 80188 processor for MAC layer functions

- Glueless PCMCIA bus interface conforming to PC Card standard—Feb. 1995

- Full PCMCIA software interface support for PC Card standard—Feb. 1995

- Glueless ISA (IEEE P996) bus interface with full support for Plug and Play release 1.0a

- Glueless SRAM interface for MAC operations, supporting up to 128 Kbytes of memory

- Glueless Flash memory interface, supporting up to 128 Kbytes of non-volatile memory for MAC control code, PCMCIA configuration

parameters, and ISA Plug and Play configuration parameters

- Provides integrated Transceiver Attachment Interface (TAI), supporting Frequency-Hopping Spread Spectrum, Direct Sequence Spread Spectrum, and infrared physical-layer interfaces

- Antenna diversity selection support

- Fabricated with submicron CMOS technology with low operating current

- Supports dual 3 V and 5 V supply applications

- Low-power mode allows reduced power consumption for critical battery-powered applications

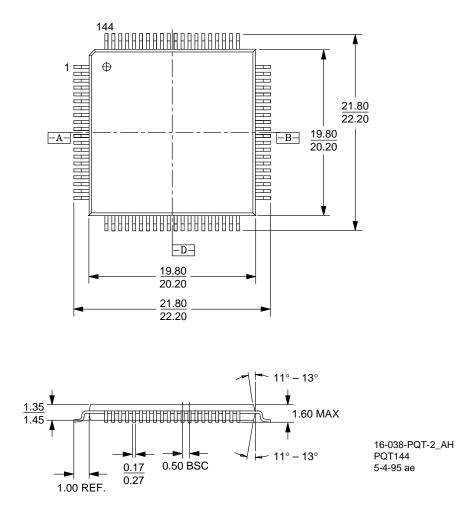

- 144-pin Thin Quad Flat Pack (TQFP) package available for space-critical applications, such as PCMCIA

- JTAG Boundary Scan (IEEE 1149.1) test access port for board-level production test

# **GENERAL DESCRIPTION**

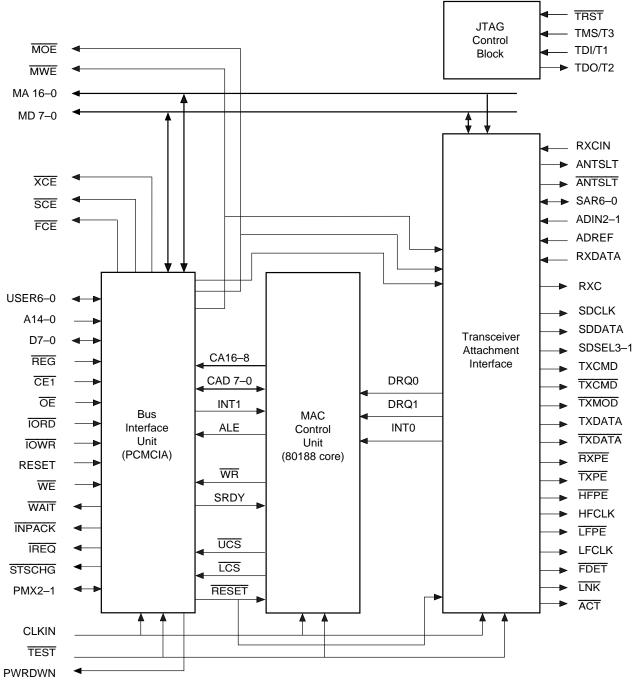

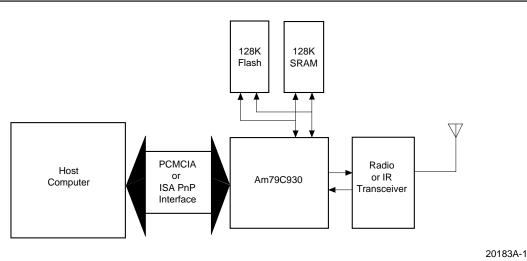

PCnet-Mobile (Am79C930) is the first in a series of mobile networking products in AMD's PCnet family. The Am79C930 device is the first single-chip wireless LAN media access controller (MAC) supporting the IEEE 802.11 (draft) standard and the Xircom Netwave<sup>™</sup> MAC protocols. The Am79C930 device is designed to have a flexible protocol engine to allow for industry standard and proprietary protocols. Protocol firmware for Xircom Netwave and IEEE 802.11 (draft) MAC protocols are supplied by AMD. It is pin-compatible with the PCMCIA bus or the ISA (Plug and Play) bus through a pin-strapping option.

The Am79C930 device contains a PCMCIA/ISA bus interface unit (BIU), a MAC control unit, and a

transceiver attachment interface (TAI). The TAI supports frequency-hopping spread spectrum, direct sequence spread spectrum, and infrared physical layer interfaces. In addition, a power down function has been incorporated to provide low standby current for powersensitive applications.

The Am79C930 device provides users with a media access controller that has flexibility (i.e., bus interface, protocol, and physical layer support) to allow the design of multiple products using a single device. By having all the necessary MAC functions on a single chip, users only need to add memory and the physical layer in order to deliver a fully functional wireless LAN connection.

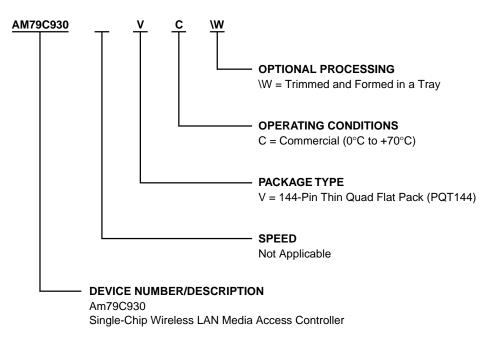

## **ORDERING INFORMATION**

### **Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (valid combination) is formed by a combination of the elements below.

| Valid Combinations |      |  |  |

|--------------------|------|--|--|

| Am79C930           | VC\W |  |  |

#### **Valid Combinations**

Valid combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

# BLOCK DIAGRAM PCMCIA Mode

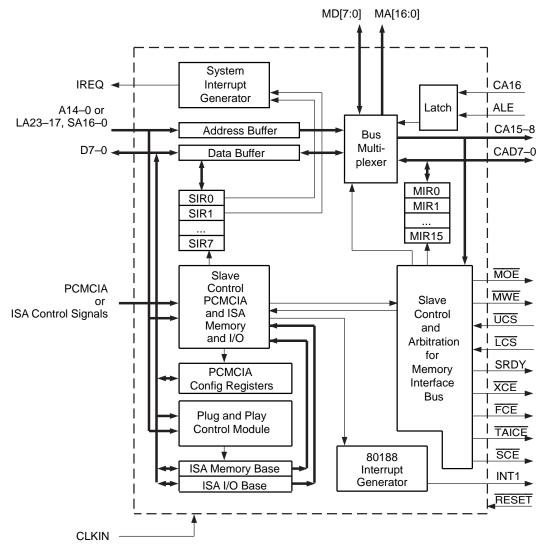

# BLOCK DIAGRAM Bus Interface Unit

# **BLOCK DIAGRAM**

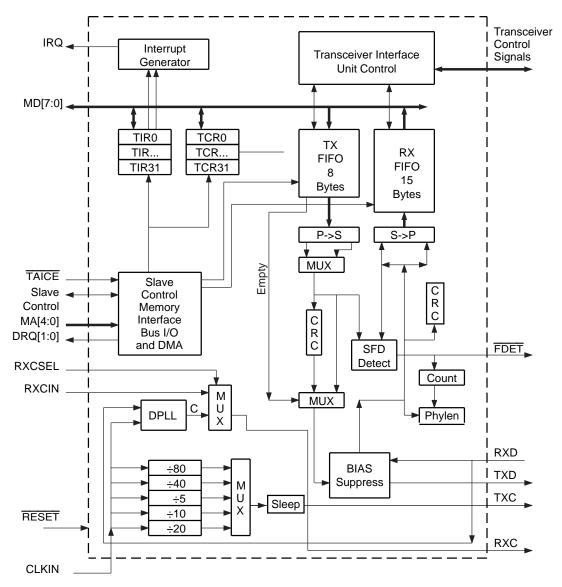

# **Transceiver Attachment Interface Unit**

# TABLE OF CONTENTS

| DISTINCTIVE CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 1                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 1                                                                  |

| ORDERING INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 2                                                                  |

| BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 3<br>. 4                                                           |

| PCMCIA BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12                                                                   |

| PCMCIA CONNECTION DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13                                                                   |

| PCMCIA PIN SUMMARY                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                      |

| PCMCIA PIN LIST                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                      |

| PCMCIA PIN FUNCTION SUMMARY                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                      |

| ISA PLUG AND PLAY BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19                                                                   |

| CONNECTION DIAGRAM         ISA Plug And Play                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                      |

| ISA PLUG AND PLAY PIN LIST<br>Listed By Pin Number<br>Listed By Pin Name                                                                                                                                                                                                                                                                                                                                                                                                       | 21                                                                   |

| ISA PLUG AND PLAY PIN SUMMARY                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23                                                                   |

| PIN DESCRIPTIONS         Pins with Internal Pull Up or Pull Down Devices         Configuration Pins         Host System Interface Pins         PCMCIA Bus Interface         ISA (IEEE P996) Bus interface         Memory Interface Pins         Clock Pins         System Management Pins         TAI Interface Pins         Other Pins         IEEE 1149.1 Test Access Port Pins         Power Supply Pins         Analog Power Supply Pins         Digital Power Supply Pins | 25<br>25<br>26<br>27<br>26<br>29<br>29<br>29<br>31<br>32<br>32<br>32 |

| Digital Power Supply Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 33                                                                   |

| Pin 2: USER3/SA16                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 34                                                                   |

| AMD |  |

|-----|--|

|     |  |

| Pin 3: USER4/LA17                                | 34 |

|--------------------------------------------------|----|

| Pin 45: STSCHG/BALE                              | 34 |

| Pin 90: USER0/RFRSH                              | 34 |

| Pin 91: USER1/IRQ12/EXTCTS/EXINT188              | 35 |

| Pin 92: USER7/IRQ11                              | 35 |

| Pin 94: RXC/IRQ10/EXTA2DST                       | 36 |

| Pin 95: USER6/IRQ5/EXTSDF                        | 36 |

| Pin 96: USER5/IRQ4/EXTCHBSY                      | 36 |

| Pin 98: ACT                                      | 37 |

| Pin 100: LNK                                     | 37 |

| Pin 101: SDCLK                                   | 38 |

| Pin 102: SDDATA                                  | 38 |

| Pin 103: SDSEL3                                  | 38 |

| Pin 105: SDSEL2                                  | 38 |

| Pin 107: SDSEL1                                  | 38 |

| Pin 115: TXC                                     | 39 |

| Pin 118: LFPE                                    | 39 |

| Pin 120: HFPE                                    | 39 |

| Pin 122: RXPE                                    | 39 |

| Pin 126: TXCMD                                   | 40 |

| Pin 129: TXPE                                    | 40 |

| Pin 131: TXMOD                                   | 40 |

| Pin 132: ANTSLT                                  | 40 |

| Pin 141: ANTSLT/LA23                             | 40 |

| Pin 142: TXCMD/LA21                              | 41 |

| Pin 143: TXDATA/LA20                             | 41 |

| Pin 144: LLOCKE/SA15                             | 41 |

| FUNCTIONAL DESCRIPTION                           | 42 |

| Basic Functions                                  | 42 |

| System Bus Interface Function                    | 42 |

| Memory Bus Interface Function                    | 42 |

| Software Interface Function                      | 42 |

| Network Interface Function                       | 42 |

| Detailed Functions                               | 42 |

| Block Level Description                          | 42 |

| Bus Interface Unit                               | 42 |

| PCMCIA Interface                                 | 43 |

| ISA (IEEE P996) Plug and Play Interface          | 44 |

| Memory Interface                                 | 45 |

| Embedded 80188                                   | 45 |

| Media Access Management                          | 45 |

| Medium Allocation                                |    |

| Initialization                                   | 46 |

| SRAM Memory Management                           | 46 |

| Flash Memory Management                          | 47 |

| Transceiver Attachment Interface Unit Management | 47 |

| Bus Interface Unit Interaction                 | . 47 |

|------------------------------------------------|------|

| Transceiver Attachment Interface Unit          | . 47 |

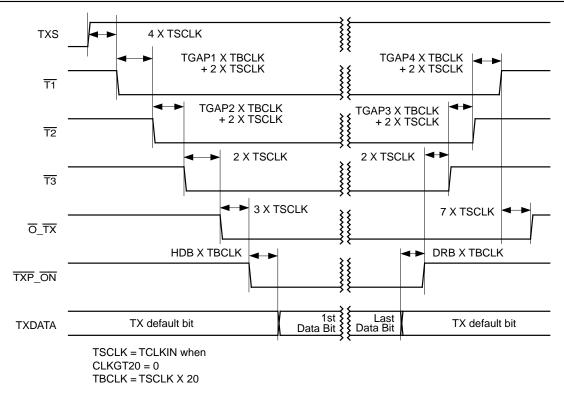

| TX FIFO                                        | . 48 |

| TX Power Ramp Control                          | . 48 |

| Am79C930-based TX Power Ramp Control           | . 48 |

| Transceiver-Based TX Power Ramp Control        | . 50 |

| TX CRC Generation                              | . 50 |

| TX Status                                      | . 50 |

| Start of Frame Delimiter Detection             | . 50 |

| RX Data Parallelization                        | . 50 |

| RX FIFO                                        | . 50 |

| RX CRC Checking                                | . 50 |

| RX Status Reporting                            | . 51 |

| Bit Ordering                                   | . 51 |

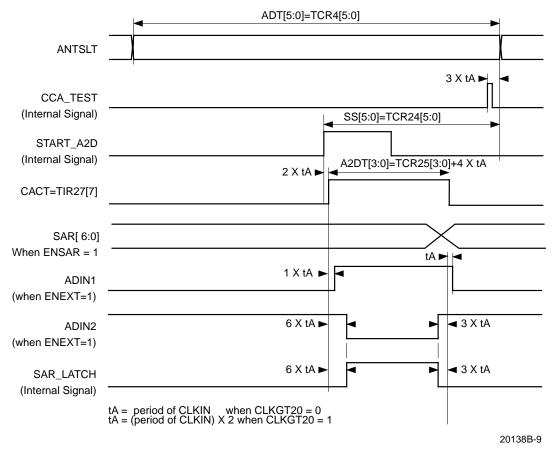

| RSSI A/D Unit                                  | . 51 |

| Physical Header Accommodation                  | . 52 |

| DC Bias Control                                | . 52 |

| Baud Determination Logic                       | . 52 |

| Clear Channel Assessment Logic                 | . 53 |

| Automatic Antenna Diversity Logic              | . 54 |

| TXC As Input                                   | . 55 |

| IEEE 1149.1 Test Access Port Interface         | . 55 |

| Boundary Scan Circuit                          | . 56 |

| TAP FSM                                        | . 56 |

| Supported Instructions                         | . 56 |

| Instruction Register and Decoding Logic        | . 56 |

| Boundary Scan Register (BSR)                   | . 56 |

| Other Data Registers                           | . 56 |

| Power Saving Modes                             | . 56 |

| Power Down Function                            | . 56 |

| Applicability to IEEE 802.11 Power Down Modes  | . 58 |

| Software Access                                | . 58 |

| Am79C930 System Interface Resources            | . 58 |

| PCMCIA Mode Resources                          | . 58 |

| PCMCIA Attribute Memory Resources.             | . 61 |

| PCMCIA I/O Resources.                          | . 62 |

| ISA Plug and Play Mode Resources               | . 63 |

| ISA Plug and Play Memory Resources             | . 64 |

| ISA Plug and Play I/O Resources.               | . 66 |

| ISA Plug and Play Register Set                 | . 68 |

| MAC Firmware Resources                         | . 70 |

| MAC (80188 core) Memory Resources              | . 70 |

| MAC (80188 core) Memory Resources Restrictions | . 72 |

| MAC (80188 core) Interrupt Channel Allocation  | . 72 |

| MAC (80188 core) DMA Channel Allocation        |      |

| DMA Channel Allocation In The 80188 Core       |      |

| Loopback Operation                             | . 73 |

| LED Support                                            | 73 |

|--------------------------------------------------------|----|

| RESET Methods                                          | 73 |

| RESET Pin                                              | 73 |

| SWRESET (SIR0[7])                                      | 73 |

| CORESET (SIR0[6])                                      | 74 |

| PCMCIA COR SRESET                                      | 74 |

| ISA PnP RESET                                          | 75 |

| SRES (TIR0[5])                                         | 75 |

| REGISTER DESCRIPTIONS                                  | 75 |

| System Interface Registers (SIR space)                 |    |

| SIR0: General Configuration Register (GCR)             | 77 |

| SIR1: Bank Switching Select Register (BSS)             |    |

| SIR2: Local Memory Address Register [7:0] (LMA)        |    |

| SIR3: Local Memory Address Register [14:8] (LMA)       | 79 |

| SIR4: I/O Data Port A (IODPA)                          |    |

| SIR5: I/O Data Port B (IODPB)                          |    |

| SIR6: I/O Data Port C (IODPC)                          |    |

| SIR7: I/O Data Port D (IODPD)                          |    |

| MAC Interface Registers (MIR Space)                    |    |

| MIR0: Processor Interface Register (PIR)               |    |

| MIR1: Power Up Clock Time [3:0] (PUCT)                 |    |

| MIR2: Power Down Length Count [7:0] (PDLC)             |    |

| MIR3: Power Down Length Count [15:8] (PDLC)            | 81 |

| MIR4: Power Down Length Count [22:16] (PDLC)           | 82 |

| MIR5: Free Count [7:0] (FCNT)                          |    |

| MIR6: Free Count [15:8] (FCNT)                         | 82 |

| MIR7: Free Count [23:16] (FCNT)                        | 82 |

| MIR8: Flash Wait States                                | 82 |

| MIR9: TCR Mask STSCHG Data                             | 83 |

| MIR10: Reserved                                        | 85 |

| MIR11: Reserved                                        |    |

| MIR12: Reserved                                        |    |

| MIR13: Reserved                                        | 85 |

| MIR14: Reserved                                        |    |

| MIR15: Reserved                                        |    |

| Transceiver Attachment Interface Registers (TIR Space) |    |

| TIR0: Network Control                                  |    |

| TIR1: Network Status                                   | 89 |

| TIR2: Serial Device                                    |    |

| TIR3: Fast Serial Port Control                         | 91 |

| TIR4: Interrupt Register 1                             | 91 |

| TIR5: Interrupt Register                               |    |

| TIR6: Interrupt Unmask Register 1                      |    |

| TIR7: Interrupt Unmask Register 2                      |    |

| TIR8: Transmit Control                                 |    |

| TIR9: Transmit Status                                  |    |

|                                                        |    |

| TIR10: TX FIFO Data Register                       | 95  |

|----------------------------------------------------|-----|

| TIR11: Transmit Sequence Control                   | 95  |

| TIR12: Byte Count Register LSB                     | 96  |

| TIR13: Byte Count Register MSB                     | 97  |

| TIR14: Byte Count Limit LSB                        | 97  |

| TIR15: Byte Count Limit MSB                        | 97  |

| TIR16: Receiver Control                            | 98  |

| TIR17: Receive Status Register                     | 98  |

| TIR18: RX FIFO Data Register                       | 99  |

| TIR19: Reserved                                    | 98  |

| TIR20: CRC32 Correct Byte Count LSB                | 99  |

| TIR21: CRC32 Correct Byte Count MSB                | 99  |

| TIR22: CRC8 Correct Byte Count LSB                 | 100 |

| TIR23: CRC8 Correct Byte Count MSB                 | 100 |

| TIR24: TCR Index Register                          | 100 |

| TIR25: Configuration Data Port                     | 101 |

| TIR26: Antenna Diversity and A/D Control           | 101 |

| TIR27: Serial Approximation Register               | 102 |

| TIR28: RSSI Lower Limit                            | 102 |

| TIR29: USER Pin Data                               |     |

| TIR30: Test Dummy Register                         |     |

| TIR31: TEST                                        |     |

| TAI Configuration Register space (TCR)             |     |

| TCR0: Network Configuration                        |     |

| TCR1: Transmit Configuration                       |     |

| TCR2: Clock Recovery                               |     |

| TCR3: Receive Configuration                        |     |

| TCR4: Antenna Diversity Timer                      |     |

| TCR5: TX Ramp Up Timing                            |     |

| TCR6: TX Ramp Down Timing                          |     |

| TCR7: Pin Data A                                   |     |

| TCR8: Start Delimiter LSB                          |     |

| TCR9: Start Delimiter CSB                          |     |

| TCR10: Start Delimiter MSB                         |     |

| TCR11: Interrupt Register 3                        |     |

| TCR12: Interrupt Unmask Register 3                 |     |

| TCR13: Pin Configuration A                         |     |

| TCR14: Pin Configuration B                         |     |

| TCR15: Pin Configuration C                         |     |

| TCR16: Baud Detect Start                           |     |

| TCR17: Baud Detect Lower Limit                     |     |

| TCR18: Baud Detect Upper Limit.                    |     |

| TCR19: Baud Detect Accept Count for Carrier Sense  |     |

| TCR20: Baud Detect Accept Count for Stop Diversity |     |

| TCR21: Baud Detect Ratio                           |     |

| TCR22: Baud Detect Accept Count                    |     |

| TCR23: Baud Detect Fail Count                      | 117 |

|     | 4 |

|-----|---|

| AMD |   |

|     |   |

| TCR24: RSSI Sample Start                                               | 117 |

|------------------------------------------------------------------------|-----|

| TCR25: RSSI Configuration                                              | 118 |

| TCR26: Reserved                                                        |     |

| TCR27: TIP LED Scramble                                                |     |

| TCR28: Clear Channel Assessment Configuration                          |     |

| TCR29: Reserved                                                        |     |

| TCR30: Pin Function and Data Rate                                      |     |

| TCR31: Device Revision       PCMCIA CCR Registers and PCMCIA CIS Space |     |

| PCMCIA CCR Registers and PCMCIA CIS Space                              |     |

| PCMCIA Card Information Structure (CIS)                                |     |

| ABSOLUTE MAXIMUM RATINGS                                               |     |

|                                                                        |     |

| OPERATING RANGES                                                       | 126 |

| DC CHARACTERISTICS                                                     |     |

| 5.0 V Am79C930 DC Characteristics                                      |     |

| 3.3 V Am79C930 DC Characteristics                                      |     |

| IEEE 1149.1 DC Characteristics (5.0 and 3.3 V)                         | 130 |

| ABSOLUTE MAXIMUM RATINGS                                               | 131 |

| OPERATING RANGES                                                       | 131 |

| AC CHARACTERISTICS                                                     | 131 |

| 5.0 and 3.3 V PCMCIA Interface AC Characteristics                      | 131 |

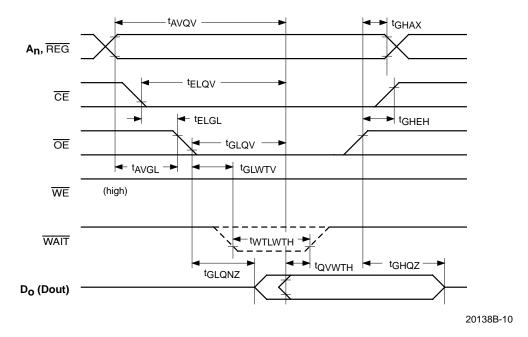

| PCMCIA MEMORY READ ACCESS                                              | 131 |

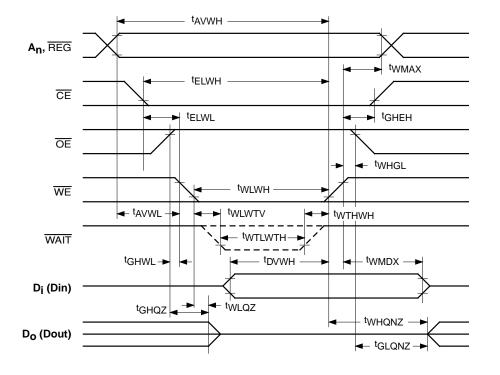

| PCMCIA MEMORY WRITE ACCESS                                             | 132 |

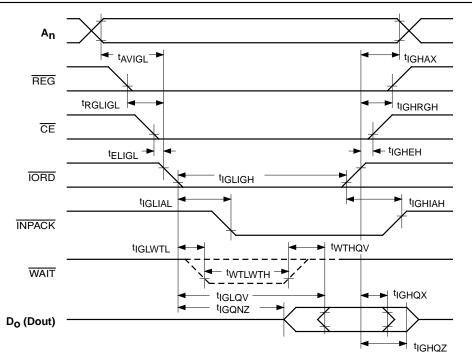

| PCMCIA I/O READ ACCESS                                                 | 133 |

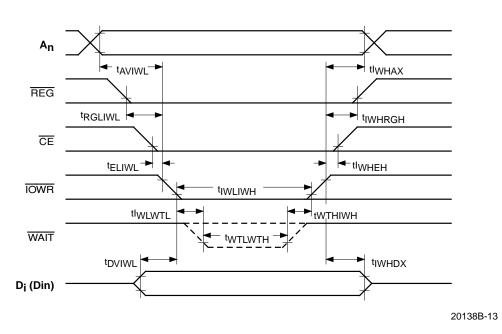

| PCMCIA I/O WRITE ACCESS                                                | 134 |

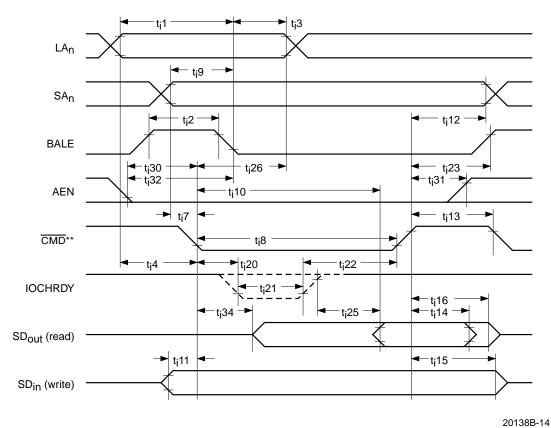

| 5.0 AND 3.3 V ISA INTERFACE AC CHARACTERISTICS                         | 135 |

| ISA ACCESS                                                             | 136 |

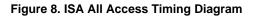

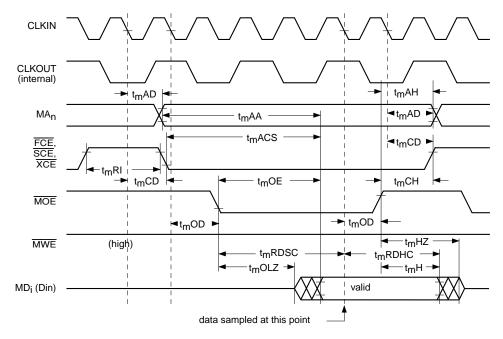

| 5.0 V MEMORY BUS INTERFACE AC CHARACTERISTICS                          | 137 |

| MEMORY BUS READ ACCESS                                                 | 137 |

| MEMORY BUS WRITE ACCESS                                                | 138 |

| 3.3 V MEMORY BUS INTERFACE AC CHARACTERISTICS                          | 139 |

| MEMORY BUS READ ACCESS                                                 | 139 |

| MEMORY BUS WRITE ACCESS                                                | 140 |

| 5.0 V TAI INTERFACE AC CHARACTERISTICS                                 | 141 |

| 3.3 V TAI INTERFACE AC CHARACTERISTICS                                 | 144 |

| 5.0 AND 3.3 V USER PROGRAMMABLE PINS AC CHARACTERISTICS                | 146 |

| 5.0 AND 3.3 V IEEE 1149.1 INTERFACE AC CHARACTERISTICS                 | 147 |

| ANALOG-TO-DIGITAL (A/D) CONVERTER CHARACTERISTICS                      | 147 |

| TIMING WAVEFORMS       148         PCMCIA Bus Interface Waveforms       148         ISA Bus Interface Waveforms       150         Memory Bus Interface Waveforms       151                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

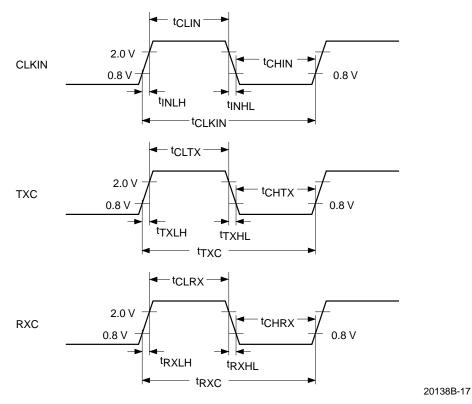

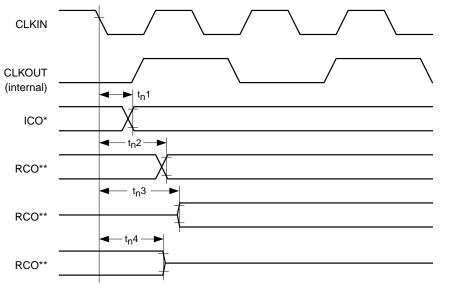

| <b>CLOCK WAVEFORMS</b>                                                                                                                                                                                         |

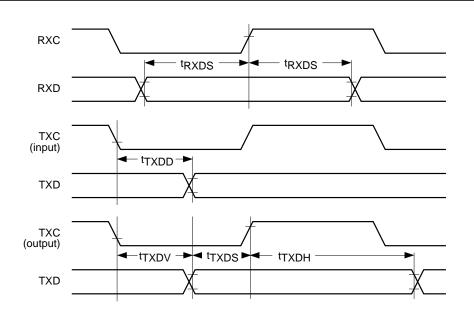

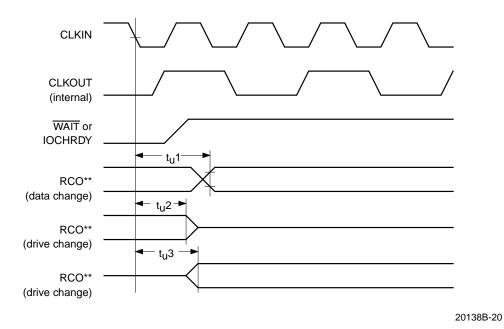

| TAI WAVEFORMS         153                                                                                                                                                                                      |

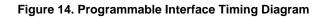

| PROGRAMMABLE INTERFACE WAVEFORMS                                                                                                                                                                               |

| <b>IEEE 1149.1 INTERFACE WAVEFORMS</b>                                                                                                                                                                         |

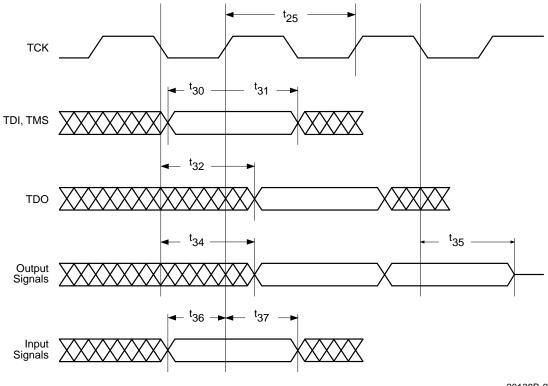

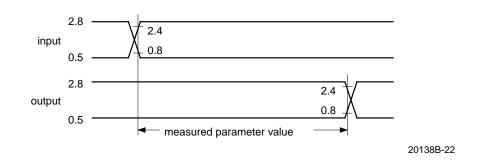

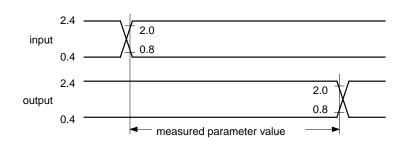

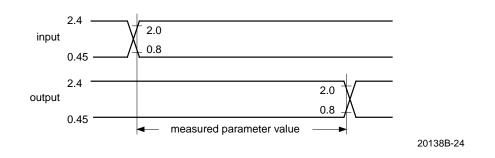

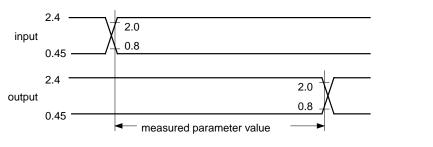

| AC TEST REFERENCE WAVEFORMS1565.0 V PCMCIA AC Test Reference Waveform1563.3 V PCMCIA AC Test Reference Waveform1565.0 V NON-PCMCIA AC Test Reference Waveform1573.3 V NON-PCMCIA AC Test Reference Waveform157 |

| PHYSICAL DIMENSIONS                                                                                                                                                                                            |

| APPENDIX A: Typical Am79C930 System Application       A-1         Device Configuration       A-1         Frame Transmission       A-2         Frame Reception       A-2                                        |

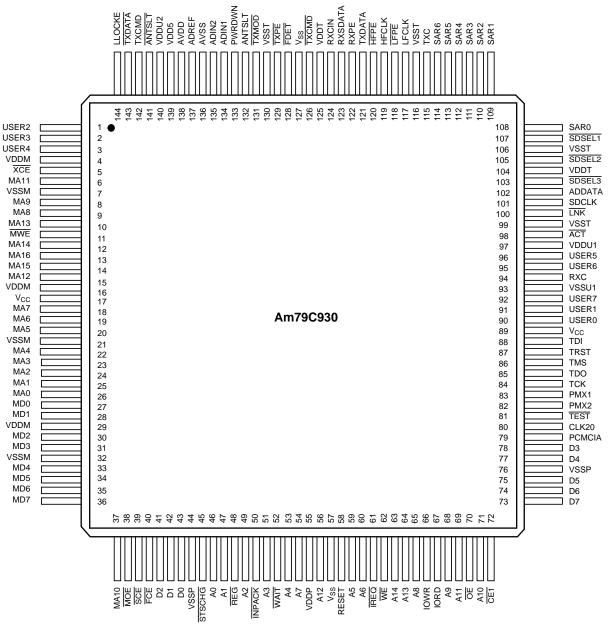

# PCMCIA CONNECTION DIAGRAM

Notes: Pin 1 is marked for orientation. NC = No Connection

# PCMCIA PIN SUMMARY

# Listed by Pin Number

| Pin No. | Pin Name        |

|---------|-----------------|---------|-----------------|---------|-----------------|---------|-----------------|

| 1       | USER2           | 37      | MA10            | 73      | D7              | 109     | SAR1            |

| 2       | USER3           | 38      | MOE             | 74      | D6              | 110     | SAR2            |

| 3       | USER4           | 39      | SCE             | 75      | D5              | 111     | SAR3            |

| 4       | VDDM            | 40      | FCE             | 76      | VSSP            | 112     | SAR4            |

| 5       | XCE             | 41      | D2              | 77      | D4              | 113     | SAR5            |

| 6       | MA11            | 42      | D1              | 78      | D3              | 114     | SAR6            |

| 7       | VSSM            | 43      | D0              | 79      | PCMCIA          | 115     | TXC             |

| 8       | MA9             | 44      | VSSP            | 80      | CLK20           | 116     | VSST            |

| 9       | MA8             | 45      | STSCHG          | 81      | TEST            | 117     | LFCLK           |

| 10      | MA13            | 46      | A0              | 82      | PMX2            | 118     | LFPE            |

| 11      | MWE             | 47      | A1              | 83      | PMX1            | 119     | HFCLK           |

| 12      | MA14            | 48      | REG             | 84      | тск             | 120     | HFPE            |

| 13      | MA16            | 49      | A2              | 85      | TDO             | 121     | TXDATA          |

| 14      | MA15            | 50      | INPACK          | 86      | TMS             | 122     | RXPE            |

| 15      | MA12            | 51      | A3              | 87      | TRST            | 123     | RXDATA          |

| 16      | VDDM            | 52      | WAIT            | 88      | TDI             | 124     | RXCIN           |

| 17      | V <sub>cc</sub> | 53      | A4              | 89      | V <sub>cc</sub> | 125     | VDDT            |

| 18      | MA7             | 54      | A7              | 90      | USER0           | 126     | TXCMD           |

| 19      | MA6             | 55      | VDDP            | 91      | USER1           | 127     | V <sub>SS</sub> |

| 20      | MA5             | 56      | A12             | 92      | USER7           | 128     | FDET            |

| 21      | VSSM            | 57      | V <sub>SS</sub> | 93      | VSSU1           | 129     | TXPE            |

| 22      | MA4             | 58      | RESET           | 94      | RXC             | 130     | VSST            |

| 23      | MA3             | 59      | A5              | 95      | USER6           | 131     | TXMOD           |

| 24      | MA2             | 60      | A6              | 96      | USER5           | 132     | ANTSLT          |

| 25      | MA1             | 61      | ĪREQ            | 97      | VDDU1           | 133     | PWRDWN          |

| 26      | MA0             | 62      | WE              | 98      | ACT             | 134     | ADIN1           |

| 27      | MD0             | 63      | A14             | 99      | VSST            | 135     | ADIN2           |

| 28      | MD1             | 64      | A13             | 100     | LNK             | 136     | AVSS            |

| 29      | VDDM            | 65      | A8              | 101     | SDCLK           | 137     | ADREF           |

| 30      | MD2             | 66      | ĪOWR            | 102     | SDDATA          | 138     | AVDD            |

| 31      | MD3             | 67      | IORD            | 103     | SDSEL3          | 139     | VDD5            |

| 32      | VSSM            | 68      | A9              | 104     | VDDT            | 140     | VDDU2           |

| 33      | MD4             | 69      | A11             | 105     | SDSEL2          | 141     | ANTSLT          |

| 34      | MD5             | 70      | ŌE              | 106     | VSST            | 142     | TXCMD           |

| 35      | MD6             | 71      | A10             | 107     | SDSEL1          | 143     | TXDATA          |

| 36      | MD7             | 72      | CE1             | 108     | SAR0            | 144     | LLOCKE          |

# PCMCIA PIN LIST

# Listed by Pin Name

| Pin Name | Pin No. | Pin Name | Pin No. | Pin Name | Pin No.   | Pin Name        | Pin No. |

|----------|---------|----------|---------|----------|-----------|-----------------|---------|

| A0       | 46      | HFPE     | 120     | ŌE       | 70        | TXMOD           | 131     |

| A1       | 47      | INPACK   | 50      | PCMCIA   | CMCIA 79  |                 | 129     |

| A10      | 71      | IORD     | 67      | PMX1     | 83        | 83 USER0        |         |

| A11      | 69      | IOWR     | 66      | PMX2     | 82        | USER1           | 91      |

| A12      | 56      | IREQ     | 61      | PWRDWN   | 133       | USER2           | 1       |

| A13      | 64      | LFCLK    | 117     | REG      | 48        | USER3           | 2       |

| A14      | 63      | LFPE     | 118     | RESET    | 58        | USER4           | 3       |

| A2       | 49      | LLOCKE   | 144     | RXC      | 94        | USER5           | 96      |

| A3       | 51      | LNK      | 100     | RXCIN    | 124       | USER6           | 95      |

| A4       | 53      | MAO      | 26      | RXDATA   | 123       | V <sub>cc</sub> | 17      |

| A5       | 59      | MA1      | 25      | RXPE     | 122       | V <sub>cc</sub> | 89      |

| A6       | 60      | MA10     | 37      | SAR0     | 108       | VDD5            | 139     |

| A7       | 54      | MA11     | 6       | SAR1     | 109       | VDDM            | 4       |

| A8       | 65      | MA12     | 15      | SAR2     | 110       | VDDM            | 16      |

| A9       | 68      | MA13     | 10      | SAR3     | 111       | VDDM            | 29      |

| ACT      | 98      | MA14     | 12      | SAR4     | 112       | VDDP            | 55      |

| ADIN1    | 134     | MA15     | 14      | SAR5     | 113       | VDDT            | 104     |

| ADIN2    | 135     | MA16     | 13      | SAR6     | 114       | VDDT            | 125     |

| ADREF    | 137     | MA2      | 24      | SCE      | 39        | VDDU1           | 97      |

| ANTSLT   | 132     | MA3      | 23      | SDCLK    | 101       | VDDU2           | 140     |

| ANTSLT   | 141     | MA4      | 22      | SDDATA   | 102       | V <sub>SS</sub> | 57      |

| AVDD     | 138     | MA5      | 20      | SDSEL1   | 107       | V <sub>SS</sub> | 127     |

| AVSS     | 136     | MA6      | 19      | SDSEL2   | 105       | VSSM            | 7       |

| CE1      | 72      | MA7      | 18      | SDSEL3   | 103       | VSSM            | 21      |

| CLK20    | 80      | MA8      | 9       | STSCHG   | 45        | VSSM            | 32      |

| D0       | 43      | MA9      | 8       | тск      | 84        | VSSP            | 44      |

| D1       | 42      | MD0      | 27      | TDI      | 88        | VSSP            | 76      |

| D2       | 41      | MD1      | 28      | TDO      | 85        | VSST            | 99      |

| D3       | 78      | MD2      | 30      | TEST     | 81        | VSST            | 106     |

| D4       | 77      | MD3      | 31      | TMS      | 86        | VSST            | 116     |

| D5       | 75      | MD4      | 33      | TRST     | 87        | VSST            | 130     |

| D6       | 74      | MD5      | 34      | тхс      | 115 VSSU1 |                 | 93      |

| D7       | 73      | MD6      | 35      | TXCMD    | 126       | WAIT            | 52      |

| FCE      | 40      | MD7      | 36      | TXCMD    | 142       | USER7           | 92      |

| FDET     | 128     | MOE      | 38      | TXDATA   | 121       | WE              | 62      |

| HFCLK    | 119     | MWE      | 11      | TXDATA   | 143       | XCE             | 5       |

# PCMCIA PIN FUNCTION SUMMARY

# **PCMCIA Pin Summary**

| No. of<br>Pins | Pin Name | Pin Name Pin Function                                                                                                                                                                            |      |

|----------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 15             | A14–A0   | PCMCIA address bus lines                                                                                                                                                                         | I    |

| 8              | D7-D0    | PCMCIA data bus lines                                                                                                                                                                            | TS2  |

| 1              | RESET    | PCMCIA bus RESET line                                                                                                                                                                            | I    |

| 1              | CE1      | Card Enable 1—used to enable the D7–0 pins for PCMCIA Read and Write accesses                                                                                                                    | I    |

| 1              | ŌE       | Output Enable—used to enable the output drivers of the Am79C930 device for PCMCIA Read accesses                                                                                                  | I    |

| 1              | WE       | Write Enable—used to indicate that the current PCMCIA cycle is a write access                                                                                                                    | I    |

| 1              | REG      | REG—used to indicate that the current PCMCIA cycle is to the Attribute<br>Memory space of the Am79C930 device                                                                                    | I    |

| 1              | INPACK   | Input Acknowledge—used to indicate that the Am79C930 device will respond to the current I/O read cycle                                                                                           | TS1  |

| 1              | WAIT     | Wait—used to delay the termination of the current PCMCIA cycle                                                                                                                                   | TS2  |

| 1              | IORD     | I/O Read—this signal is asserted by the PCMCIA host system whenever an I/O read operation occurs                                                                                                 |      |

| 1              | IOWR     | I/O Write—this signal is asserted by the PCMCIA host system whenever an I/O write operation occurs                                                                                               | I    |

| 1              | IREQ     | Interrupt Request—this line is asserted when the Am79C930 device needs servicing from the software                                                                                               | PTS3 |

| 1              | STSCHG   | Status Change—PCMCIA output used only for WAKEUP signaling                                                                                                                                       | PTS1 |

| 1              | PCMCIA   | PCMCIA mode—selects PCMCIA or ISA Plug and Play mode                                                                                                                                             | I    |

| 1              | PWRDWN   | Powerdown—indicates that device is in the power down mode                                                                                                                                        | TP1  |

| 17             | MA16-0   | Memory Address Bus—these lines are used to address locations in the Flash device, the SRAM device, and an extra peripheral device that are contained within an Am79C930-based design             | TP1  |

| 8              | MD7-0    | Memory Data Bus—these lines are used to write and read data to/from Flash, SRAM, and/or an extra peripheral device within an Am79C930-based design                                               | TS1  |

| 1              | FCE      | Flash Chip Enable—this signal becomes asserted when the Flash device has been addressed by either the 80188 core of the Am79C930 device or by the software through the PCMCIA interface          | TP1  |

| 1              | SCE      | SRAM Chip Enable—this signal becomes asserted when the SRAM device<br>has been addressed by either the 80188 core of the Am79C930 device or by<br>the software through the PCMCIA interface      | TP1  |

| 1              | XCE      | eXtra Chip Enable—this signal becomes asserted when the extra peripheral device has been addressed by the 80188 core of the Am79C930 device (XCE is not accessible through the system interface) | TP1  |

| 1              | MOE      | Memory Output Enable—this signal becomes asserted during reads of devices located on the memory interface bus                                                                                    | TP1  |

| 1              | MWE      | Memory Write Enable—this signal becomes asserted during writes to devices located on the memory interface bus                                                                                    | TP1  |

| 1              | тск      | Test Clock—this is the clock signal for IEEE 1149.1 testing                                                                                                                                      | I    |

| 1              | TDI      | Test Data In-this is the data input signal for IEEE 1149.1 testing                                                                                                                               | I    |

# PCMCIA PIN FUNCTION SUMMARY (continued) PCMCIA Pin Summary (continued)

| No. of<br>Pins | Pin Name       | Pin Function                                                                                                    | Pin Style |

|----------------|----------------|-----------------------------------------------------------------------------------------------------------------|-----------|

| 1              | TDO            | Test Data Out-this is the data output signal for IEEE 1149.1 testing                                            | TS1       |

| 1              | TMS            | Test Mode Select—this is the test mode select for IEEE 1149.1 testing                                           | I         |

| 1              | TRST           | Test Reset—this is the reset signal for IEEE 1149.1 testing                                                     | I         |

| 1              | USER7          | User-programmable pin                                                                                           | PTS3      |

| 1              | RXC            | Receive Clock—provides decode receive clock                                                                     | PTS3      |

| 1              | TEST           | Test pin—when asserted, this pin places the Am79C930 device into a nonstandard factory-only test mode           | I         |

| 1              | CLKIN          | Clock input to drive BIU, 80188 core, and TAI, supplying network data rate information                          | I         |

| 2              | PMX1–2         | Power Management Xtal—32-kHz Xtal input for sleep timer reference                                               | I/XO      |

| 1              | ТХС            | Transmit Clock—may be configured either as input or output                                                      | TS1       |

| 1              | LFPE           | Low Frequency Power Enable—used to power up the low-frequency section of the transceiver                        | PTS1      |

| 1              | LFCLK          | Low Frequency Clock—a reference signal for the transceiver synthesizer                                          | TS1       |

| 1              | LLOCKE         | Low Frequency Synthesizer Lock—a programmable signal                                                            | PTS1      |

| 1              | HFPE           | High Frequency Power Enable—used to power up the high-frequency section of the transceiver                      |           |

| 1              | HFCLK          | High Frequency Clock—a reference signal for the transceiver synthesizer                                         | TS1       |

| 2              | ANTSLT, ANTSLT | Antenna Select—used to select between two antennas                                                              | PTS1      |

| 2              | TXCMD, TXCMD   | Transmit Command—used to select the transmit path in the transceiver                                            | TP1, PTS1 |

| 1              | TXPE           | Transmit Power Enable—used to power up the transmit section of the transceiver                                  | TP1       |

| 2              | TXDATA, TXDATA | Transmit Data—supplies the transmit data stream to the transceiver                                              | TP1, PTS1 |

| 1              | TXMOD          | Transmit Modulation Enable—enables the modulation of transmit data                                              | TP1       |

| 1              | RXPE           | Receive Power Enable—enables the receive function of the transceiver                                            | PTS1      |

| 1              | RXDATA         | Receive Data—accepts receive data in NRZ format from the transceiver                                            | I         |

| 1              | FDET           | Frame Detect—start of frame delimiter detection indication                                                      | TS1       |

| 1              | RXCIN          | Receive Clock Input—optional clock input that allows for an external PLL                                        | IPU       |

| 1              | SDCLK          | Serial Data Clock—clock output used to access serial peripheral devices                                         | PTS1      |

| 1              | SDDATA         | Serial Data Data—data pin used to access serial peripheral devices                                              | PTS1      |

| 3              | SDSEL3-SDSEL1  | Serial Data Select—chip select outputs used to select serial peripheral devices                                 | PTS1      |

| 1              | ACT            | Activity LED—output capable of driving an LED                                                                   | PTS2      |

| 1              | LNK            | Link LED—output capable of driving an LED                                                                       | PTS2      |

| 1              | ADREF          | A/D Reference—an input that can be used to set the analog reference voltage for the internal A/D converter      | I         |

| 7              | SAR6-SAR0      | Serial Approximation Register—supplies the value of the serial approximation register used in the A/D converter | TS1       |

# PCMCIA PIN FUNCTION SUMMARY (continued) PCMCIA Pin Summary (continued)

| No. of<br>Pins | Pin Name        | Pin Function                                                                                | Pin Style  |

|----------------|-----------------|---------------------------------------------------------------------------------------------|------------|

| 2              | ADIN1–2         | Comparator—A/D comparator inputs                                                            | TS1        |

| 12             | V <sub>cc</sub> | Power                                                                                       | I          |

| 13             | GND             | Ground                                                                                      | I          |

| 7              | USER0-USER6     | User-definable I/O pins with direct accessibility and control through TCR and TIR registers | PTS3, PTS1 |

# **Output Driver Types**

| Name | Туре                        | I <sub>OL</sub> | I <sub>он</sub> | Load   |

|------|-----------------------------|-----------------|-----------------|--------|

| TP1  | Totem pole                  | 4 mA            | –4 mA           | 50 pF  |

| TS1  | Tri-state                   | 4 mA            | -4 mA           | 50 pF  |

| TS2  | Tri-state                   | 24 mA           | -4 mA           | 120 pF |

| PTS1 | User-programmable tri-state | 4 mA            | -4 mA           | 50 pF  |

| PTS2 | User-programmable tri-state | 12 mA           | -4 mA           | 50 pF  |

| PTS3 | User-programmable tri-state | 24 mA           | –4 mA           | 120 pF |

| OD2  | Open drain                  | 24 mA           | -4 mA           | 120 pF |

| XO   | Xtal amplifier output       | NA              | NA              | 50 pF  |

# Input Types

| Name | Туре                                    | Size of Pullup | Size of Pulldown |

|------|-----------------------------------------|----------------|------------------|

| I    | Input                                   | NA             | NA               |

| IPU  | IPU Input with internal pullup device   |                | NA               |

| IPD  | IPD Input with internal pulldown device |                | >50K Ω           |

# ISA PLUG AND PLAY BLOCK DIAGRAM

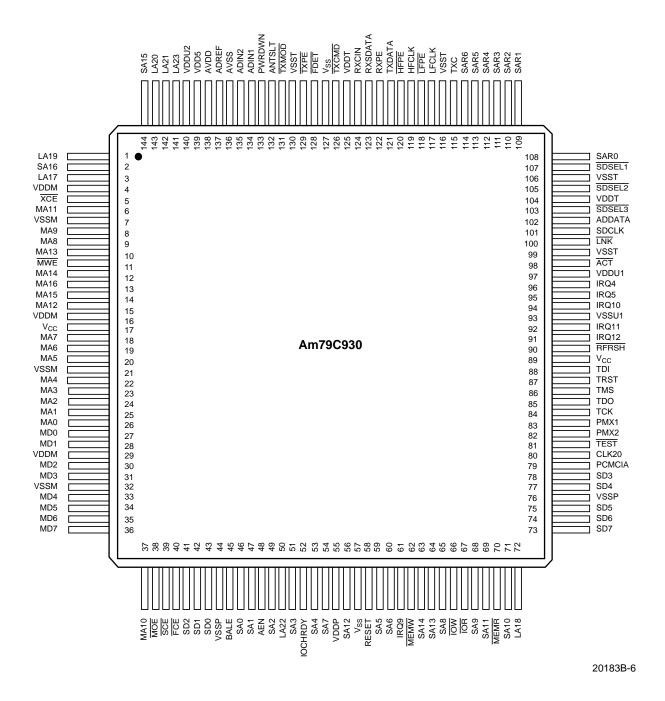

# ISA PLUG AND PLAY CONNECTION DIAGRAM

*Notes: Pin 1 is marked for orientation. NC = No Connection*

# ISA PLUG AND PLAY PIN LIST

# Listed by Pin Number

| Pin No. | Pin Name        |

|---------|-----------------|---------|-----------------|---------|-----------------|---------|-----------------|

| 1       | LA19            | 37      | MA10            | 73      | SD7             | 109     | SAR1            |

| 2       | SA16            | 38      | MOE             | 74      | SD6             | 110     | SAR2            |

| 3       | LA17            | 39      | SCE             | 75      | SD5             | 111     | SAR3            |

| 4       | VDDM            | 40      | FCE             | 76      | VSSP            | 112     | SAR4            |

| 5       | XCE             | 41      | SD2             | 77      | SD4             | 113     | SAR5            |

| 6       | MA11            | 42      | SD1             | 78      | SD3             | 114     | SAR6            |

| 7       | VSSM            | 43      | SD0             | 79      | PCMCIA          | 115     | TXC             |

| 8       | MA9             | 44      | VSSP            | 80      | CLK20           | 116     | VSST            |

| 9       | MA8             | 45      | BALE            | 81      | TEST            | 117     | LFCLK           |

| 10      | MA13            | 46      | SA0             | 82      | PMX2            | 118     | LFPE            |

| 11      | MWE             | 47      | SA1             | 83      | PMX1            | 119     | HFCLK           |

| 12      | MA14            | 48      | AEN             | 84      | тск             | 120     | HFPE            |

| 13      | MA16            | 49      | SA2             | 85      | TDO             | 121     | TXDATA          |

| 14      | MA15            | 50      | LA22            | 86      | TMS             | 122     | RXPE            |

| 15      | MA12            | 51      | SA3             | 87      | TRST            | 123     | RXDATA          |

| 16      | VDDM            | 52      | IOCHRDY         | 88      | TDI             | 124     | RXCIN           |

| 17      | V <sub>CC</sub> | 53      | SA4             | 89      | V <sub>CC</sub> | 125     | VDDT            |

| 18      | MA7             | 54      | SA7             | 90      | RFRSH           | 126     | TXCMD           |

| 19      | MA6             | 55      | VDDP            | 91      | IRQ12           | 127     | V <sub>SS</sub> |

| 20      | MA5             | 56      | SA12            | 92      | IRQ11           | 128     | FDET            |

| 21      | VSSM            | 57      | V <sub>SS</sub> | 93      | VSSU1           | 129     | TXPE            |

| 22      | MA4             | 58      | RESET           | 94      | IRQ10           | 130     | VSST            |

| 23      | MA3             | 59      | SA5             | 95      | IRQ5            | 131     | TXMOD           |

| 24      | MA2             | 60      | SA6             | 96      | IRQ4            | 132     | ANTSLT          |

| 25      | MA1             | 61      | IRQ9            | 97      | VDDU1           | 133     | PWRDWN          |

| 26      | MA0             | 62      | MEMW            | 98      | ACT             | 134     | ADIN1           |

| 27      | MD0             | 63      | SA14            | 99      | VSST            | 135     | ADIN2           |

| 28      | MD1             | 64      | SA13            | 100     | LNK             | 136     | AVSS            |

| 29      | VDDM            | 65      | SA8             | 101     | SDCLK           | 137     | ADREF           |

| 30      | MD2             | 66      | IOW             | 102     | SDDATA          | 138     | AVDD            |

| 31      | MD3             | 67      | IOR             | 103     | SDSEL3          | 139     | VDD5            |

| 32      | VSSM            | 68      | SA9             | 104     | VDDT            | 140     | VDDU2           |

| 33      | MD4             | 69      | SA11            | 105     | SDSEL2          | 141     | LA23            |

| 34      | MD5             | 70      | MEMR            | 106     | VSST            | 142     | LA21            |

| 35      | MD6             | 71      | SA10            | 107     | SDSEL1          | 143     | LA20            |

| 36      | MD7             | 72      | LA18            | 108     | SAR0            | 144     | SA15            |

# ISA PLUG AND PLAY PIN LIST

# Listed by Pin Name

| Pin Name | Pin No. | Pin Name | Pin No. | Pin Name | Pin No. | Pin Name        | Pin No. |

|----------|---------|----------|---------|----------|---------|-----------------|---------|

| ĀCT      | 98      | MA11     | 6       | SA1      | 47      | SDSEL2          | 105     |

| ADIN1    | 134     | MA12     | 15      | SA10     | 71      | SDSEL3          | 103     |

| ADIN2    | 135     | MA13     | 10      | SA11     | 69      | тск             | 84      |

| ADREF    | 137     | MA14     | 12      | SA12     | 56      | TDI             | 88      |

| AEN      | 48      | MA15     | 14      | SA12     | 56      | TDO             | 85      |

| ANTSLT   | 132     | MA16     | 13      | SA13     | 64      | TEST            | 81      |

| AVDD     | 138     | MA2      | 24      | SA14     | 63      | TMS             | 86      |

| AVSS     | 136     | MA3      | 23      | SA15     | 144     | TRST            | 87      |

| BALE     | 45      | MA4      | 22      | SA16     | 2       | ТХС             | 115     |

| CLK20    | 80      | MA5      | 20      | SA2      | 49      | TXCMD           | 126     |

| FCE      | 40      | MA6      | 19      | SA3      | 51      | TXDATA          | 121     |

| FDET     | 128     | MA7      | 18      | SA4      | 53      | TXMOD           | 131     |

| HFCLK    | 119     | MA8      | 9       | SA5      | 59      | TXPE            | 129     |

| HFPE     | 120     | MA9      | 8       | SA6      | 60      | V <sub>cc</sub> | 17      |

| IOCHRDY  | 52      | MD0      | 27      | SA7      | 54      | V <sub>cc</sub> | 89      |

| ĪOR      | 67      | MD1      | 28      | SA8      | 65      | VDD5            | 139     |

| ĪOW      | 66      | MD2      | 30      | SA9      | 68      | VDDM            | 4       |

| IRQ10    | 94      | MD3      | 31      | SAR0     | 108     | VDDM            | 16      |

| IRQ11    | 92      | MD4      | 33      | SAR1     | 109     | VDDM            | 29      |

| IRQ12    | 91      | MD5      | 34      | SAR2     | 110     | VDDP            | 55      |

| IRQ4     | 96      | MD6      | 35      | SAR3     | 111     | VDDT            | 104     |

| IRQ5     | 95      | MD7      | 36      | SAR4     | 112     | VDDT            | 125     |

| IRQ9     | 61      | MEMR     | 70      | SAR5     | 113     | VDDU1           | 97      |

| LA17     | 3       | MEMW     | 62      | SAR6     | 114     | VDDU2           | 140     |

| LA18     | 72      | MOE      | 38      | SCE      | 39      | V <sub>SS</sub> | 57      |

| LA19     | 1       | MWE      | 11      | SD0      | 43      | V <sub>SS</sub> | 127     |

| LA20     | 143     | PCMCIA   | 79      | SD1      | 42      | VSSM            | 7       |

| LA21     | 142     | PMX1     | 83      | SD2      | 41      | VSSM            | 32      |

| LA22     | 50      | PMX2     | 82      | SD3      | 78      | VSSP            | 44      |

| LA23     | 141     | PWRDWN   | 133     | SD4      | 77      | VSSP            | 76      |

| LFCLK    | 117     | RESET    | 58      | SD5      | 75      | VSST            | 99      |

| LFPE     | 118     | RFRSH    | 90      | SD6      | 74      | VSST            | 106     |

| LNK      | 100     | RXCIN    | 124     | SD7      | 73      | VSST            | 116     |

| MA0      | 26      | RXDATA   | 123     | SDCLK    | 101     | VSST            | 130     |

| MA1      | 25      | RXPE     | 122     | SDDATA   | 102     | VSSU1           | 93      |

| MA10     | 37      | SA0      | 46      | SDSEL1   | 107     | XCE             | 5       |

# ISA PLUG AND PLAY PIN SUMMARY

| No. of<br>Pins | Pin Name               | Pin Function                                                                                                                                                                                     | Pin Style |

|----------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 7              | LA23–LA17              | ISA upper address bus lines                                                                                                                                                                      |           |

| 17             | SA16-SA0               | ISA lower address bus lines                                                                                                                                                                      | I         |

| 8              | SD7-SD0                | ISA data bus lines                                                                                                                                                                               | TS2       |

| 1              | RESET                  | RESET input                                                                                                                                                                                      | I         |

| 1              | MEMR                   | Memory Read—used to enable the output drivers of the Am79C930 device for ISA bus memory read accesses                                                                                            | I         |

| 1              | MEMW                   | Memory Write—used to indicate that the current ISA bus cycle is a memory write access                                                                                                            | I         |

| 1              | AEN                    | Address Enable—used to indicate that the current ISA bus I/O address is valid                                                                                                                    | I         |

| 1              | BALE                   | Bus Address Latch Enable—used to indicate that the ISA address lines are valid                                                                                                                   | Ι         |

| 1              | IOCHRDY                | I/O Channel Ready—used to delay the termination of the current ISA bus cycle                                                                                                                     | TS2       |

| 1              | ĪOR                    | I/O Read—this signal is asserted by the ISA host system whenever an I/O read operation occurs                                                                                                    | I         |

| 1              | ĪOW                    | I/O Write—this signal is asserted by the ISA host system whenever an I/O write operation occurs                                                                                                  | I         |

| 6              | IRQ4, 5, 9, 10, 11, 12 | Interrupt Request—this line is asserted when the Am79C930 device needs servicing from the software                                                                                               | PTS3/OD2  |

| 1              | RFRSH                  | Refresh—indicates that the current ISA bus cycle is a refresh operation                                                                                                                          | I         |

| 1              | PCMCIA                 | PCMCIA mode—selects PCMCIA or ISA Plug and Play mode                                                                                                                                             | I         |

| 1              | PWRDWN                 | Powerdown—indicates that device is in the power down mode                                                                                                                                        | TP1       |

| 17             | MA16–0                 | Memory Address Bus—these lines are used to address locations in the Flash device, the SRAM device, and an extra peripheral device that are contained within an Am79C930-based design             | TP1       |

| 8              | MD7-0                  | Memory Data Bus—these lines are used to write and read data to/from Flash, SRAM, and/or an extra peripheral device within an Am79C930-based design                                               | TS1       |

| 1              | FCE                    | Flash Chip Enable—this signal becomes asserted when the Flash device has been addressed by either the 80188 core of the Am79C930 device or by the software through the PCMCIA interface          | TP1       |

| 1              | SCE                    | SRAM Chip Enable—this signal becomes asserted when the SRAM device<br>has been addressed by either the 80188 core of the Am79C930 device or by<br>the software through the PCMCIA interface      | TP1       |

| 1              | XCE                    | eXtra Chip Enable—this signal becomes asserted when the extra peripheral device has been addressed by the 80188 core of the Am79C930 device (XCE is not accessible through the system interface) | TP1       |

| 1              | MOE                    | Memory Output Enable—this signal becomes asserted during reads of devices located on the memory interface bus                                                                                    | TP1       |

| 1              | MWE                    | Memory Write Enable—this signal becomes asserted during writes to devices located on the memory interface bus                                                                                    | TP1       |

| 1              | тск                    | Test Clock—this is the clock signal for IEEE 1149.1 testing                                                                                                                                      | I         |

| 1              | TDI                    | Test Data In-this is the data input signal for IEEE 1149.1 testing                                                                                                                               | I         |

| 1              | TDO                    | Test Data Out—this is the data output signal for IEEE 1149.1 testing                                                                                                                             | TS1       |

| 1              | TMS                    | Test Mode Select—this is the test mode select for IEEE 1149.1 testing                                                                                                                            | I         |

| 1              | TRST                   | Test Reset—this is the reset signal for IEEE 1149.1 testing                                                                                                                                      | l         |

| 1              | TEST                   | Test pin—when asserted, this pin places the Am79C930 device into a non-IEEE 1149.1 test mode                                                                                                     | I         |

| 1              | CLKIN                  | Clock input to drive BIU, 80188 core, and TAI, supplying network data rate information                                                                                                           | I         |

| 2              | PMX1–2                 | Power Management Xtal—32-kHz Xtal input for sleep timer reference                                                                                                                                | I/XO      |

# ISA PLUG AND PLAY PIN SUMMARY (continued)

| No. of<br>Pins | Pin Name        | Pin Function                                                                                                    |      |

|----------------|-----------------|-----------------------------------------------------------------------------------------------------------------|------|

| 1              | TXC             | Transmit Clock—may be configured either as input or output                                                      | TS1  |

| 1              | LFPE            | Low Frequency Power Enable—used to power up the low-frequency section of the transceiver                        | PTS1 |

| 1              | LFCLK           | Low Frequency Clock—a reference signal for the transceiver synthesizer                                          | TS1  |

| 1              | HFPE            | High Frequency Power Enable—used to power up the high-frequency section of the transceiver                      | PTS1 |

| 1              | HFCLK           | High Frequency Clock—a reference signal for the transceiver synthesizer                                         | TS1  |

| 1              | ANTSLT          | Antenna Select—used to select between two antennas                                                              | PTS1 |

| 1              | TXCMD           | Transmit Command—used to select the transmit path in the transceiver                                            | TP1  |

| 1              | TXPE            | Transmit Power Enable—used to power up the transmit section of the transceiver                                  | TP1  |

| 1              | TXDATA          | Transmit Data—supplies the transmit data stream to the transceiver                                              | TP1  |

| 1              | TXMOD           | Transmit Modulation Enable—enables the modulation of transmit data                                              |      |

| 1              | RXPE            | Receive Power Enable—enables the receive function of the transceiver                                            | PTS1 |

| 1              | RXDATA          | Receive Data—accepts receive data in NRZ format from the transceiver                                            | I    |

| 1              | FDET            | Frame Detect—start of frame delimiter detection indication                                                      | TS1  |

| 1              | RXCIN           | Receive Clock Input—optional clock input that allows for an external PLL                                        | IPU  |

| 1              | SDCLK           | Serial Data Clock—clock output used to access serial peripheral devices                                         | PTS1 |

| 1              | SDDATA          | Serial Data Data—data pin used to access serial peripheral devices                                              | PTS1 |

| 3              | SDSEL3-SDSEL1   | Serial Data Select—chip select outputs used to select serial peripheral devices                                 | PTS1 |

| 1              | ACT             | Activity LED—output capable of driving an LED                                                                   | PTS2 |

| 1              | LNK             | Link LED—output capable of driving an LED                                                                       | PTS2 |

| 1              | ADREF           | A/D Reference—an input that can be used to set the analog reference voltage for the internal A/D converter      |      |

| 7              | SAR6-SAR0       | Serial Approximation Register—supplies the value of the serial approximation register used in the A/D converter |      |

| 2              | ADIN1–2         | Comparator—A/D comparator inputs                                                                                | TS1  |

| 12             | V <sub>cc</sub> | Power                                                                                                           | I    |

| 13             | GND             | Ground                                                                                                          | I    |

# Output Driver Types

| Name | Туре                        | I <sub>OL</sub> | I <sub>он</sub> | load   |

|------|-----------------------------|-----------------|-----------------|--------|

| TP1  | Totem pole                  | 4 mA            | -4 mA           | 50 pF  |

| TS1  | Tri-state                   | 4 mA            | -4 mA           | 50 pF  |

| TS2  | Tri-state                   | 24 mA           | -4 mA           | 120 pF |

| PTS1 | User-programmable tri-state | 4 mA            | -4 mA           | 50 pF  |

| PTS2 | User-programmable tri-state | 12 mA           | -4 mA           | 50 pF  |

| PTS3 | User-programmable tri-state | 24 mA           | -4 mA           | 120 pF |

| OD2  | Open drain                  | 24 mA           | -4 mA           | 120 pF |

| XO   | Xtal amplifier              | Output          | NA              | NA     |

# Input Types

| Name | Name Type                               |    | Size of Pulldown |

|------|-----------------------------------------|----|------------------|

| I    | Input                                   | NA | NA               |

| IPU  | IPU Input with internal pullup device   |    | NA               |

| IPD  | IPD Input with internal pulldown device |    | >50K Ω           |

Input

## PIN DESCRIPTIONS Pins with Internal Pull Up or Pull Down Devices

Several pins of the Am79C930 device include internal pull up or pull down devices. With the exception of the RESET pin, these pins are fully programmable as inputs or outputs when the PCMCIA mode has been selected. A subset of these pins is programmable when the ISA Plug and Play mode has been selected. These pins will come up after RESET in the high impedance state with the pull up or pull down device actively determining the value of the pin, unless an external driving source overdrives the pull up or pull down device. VINITDN bit (MIR9[2]) is used to turn off all pull up and pull down devices.

The following list indicates those pins that contain pull up and pull down devices:

| PCMCIA Mode<br>Pin Name | Internal Device<br>Type | Size of Internal<br>Device |

|-------------------------|-------------------------|----------------------------|

| USER[6]/IRQ5            | pull up                 | > 100K Ω                   |

| USER[5]/IRQ4            | pull up                 | > 100K Ω                   |

| USER[4]/LA17            | pull up                 | > 100K Ω                   |

| USER[3]/SA16            | pull up                 | > 100K Ω                   |

| USER[2]/LA19            | pull up                 | > 100K Ω                   |

| USER[1]/IRQ12           | pull down               | > 100K Ω                   |

| USER[0]/RFRSH           | pull down               | > 100K Ω                   |

| LLOCKE/SA15             | pull down               | > 100K Ω                   |

| ANTSLT/LA23             | pull up                 | > 100K Ω                   |

| TXDATA/LA20             | pull up                 | > 100K Ω                   |

| TXCMD/LA21              | pull down               | > 100K Ω                   |

| RXC/IRQ10               | pull up                 | > 100K Ω                   |

| USER7/IRQ11             | pull up                 | > 100K Ω                   |

| LFPE                    | pull up                 | > 100K Ω                   |

| HFPE                    | pull up                 | > 100K Ω                   |

| RXPE                    | pull up                 | > 100K Ω                   |

| ANTSLT                  | pull down               | > 100K Ω                   |

| TXCMD                   | pull up                 | > 100K Ω                   |

| TXPE                    | pull up                 | > 100K Ω                   |

| SDCLK                   | pull up                 | > 100K Ω                   |

| SDDATA                  | pull up                 | > 100K Ω                   |

| SDSEL[3]                | pull up                 | > 100K Ω                   |

| SDSEL[2]                | pull up                 | > 100K Ω                   |

| SDSEL[1]                | pull up                 | > 100K Ω                   |

| ACT                     | pull up                 | > 100K Ω                   |

| LNK                     | pull up                 | > 100K Ω                   |

| TXMOD                   | pull up                 | > 100K Ω                   |

| STSCHG/BALE             | pull up                 | > 100K Ω                   |

| TXC                     | pull up                 | > 100K Ω                   |